芯片未來怎么發展?IMEC這樣看

芯片未來怎么發展?IMEC這樣看

未來幾年將在工業中引入哪些邏輯 CMOS 縮放的新創新?

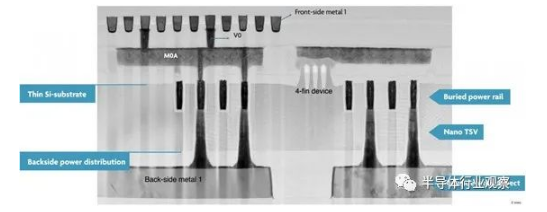

在imec看來,使用晶圓背面為設備供電是下一個主要的性能提升器。晶圓正面的傳統金屬層將用于路由信號,而晶圓背面的金屬層將用于供電。將電源傳輸和信號路由分開可以降低電源中的壓降(從而提高性能)并減少前端金屬路由的擁塞。

英特爾也宣布,他們將在 2nm 節點上引入這種帶有納米片器件的器件。

TEM 圖像顯示了連接到晶圓背面和正面的縮放 FinFET。

IMEC進一步指出,納米片和forksheets之外的器件架構是complementary FETs (CFET),其中 N 和 P 器件使用復雜的集成相互堆疊。imec強調。未來還有幾種潛在的 CFET 類型,但他們正處于探索的早期階段。

在后端金屬化中,IMEC表示,銅雙鑲嵌集成將讓位于高縱橫比金屬蝕刻以形成低于 20nm 間距的圖案線。而IMEC一直專注于將釕用于直接金屬蝕刻。為了降低電阻,釕的縱橫比將隨著氣隙的增加而增加,以減少電容的影響。這些更改將確保后端 RC(電阻-電容)擴展路線圖在多個節點上繼續進行。

IMEC方面認為,邏輯和內存組件的擴展變得越來越困難。即使由于集成復雜性導致成本繼續增加,節點到節點的改進也在減少。在設計方面,有一種趨勢是為每個功能(如神經處理、圖形、視頻等)創建更多特定領域的加速器,并且更加關注硬件-軟件協同優化以在系統級別獲得更多收益。

還有一個驅動力來確定特定技術以解決系統瓶頸,例如內存墻(如何以高帶寬獲取數據,以足夠的速度和足夠低的功率為邏輯內核供電),電源墻(如何有效地處理電力傳輸和散熱)或數據通信瓶頸(如何確保有線、光子學和無線基礎設施能夠處理成倍增長的數據流量),而不是依賴現成的通用技術。

據IMEC所說,在 AMD 的 V-cache 技術等高性能計算空間中有一些示例,其中使用 3D 集成使額外的 SRAM 內存更接近 CPU。另一個例子是使用硅中介層橋接連接 Apple M1 Ultra 片上系統 (SoC) 中的兩個 CPU 芯片。

隨著光學 IO 系統中數據帶寬的增加,行業還在大力推動利用不同的 3D 和 2.5D 技術共同封裝電子和光子 IC,以減少寄生電阻。對于3D 和 2.5D 連接,根據連接密度、成本和復雜性,有多種選擇。設備、計量和 EDA 基礎設施也需要成熟,以推動標準化并降低成本以實現更廣泛的采用。

IMEC表示,隨著光學 IO 支持的數據速率增加,電子 IC 和光子 IC 使用共同封裝的光學器件更緊密地集成以減少寄生效應。而他們正在開發新模塊,以使共同封裝的光學器件成為現實。

在主動式存儲器計劃中,IMEC不斷提高 IGZO(銦鎵鋅氧化物)器件的器件性能和可靠性,這將在未來的規模化 DRAM 架構中發揮關鍵作用。在IMEC的存儲計劃中,他們將繼續為存儲應用推動傳統的全方位門控3D NAND 閃存擴展路線圖。

轉載微信公眾號:半導體行業觀察

聲明:本文版權歸原作者所有,轉發僅為更大范圍傳播,若有異議請聯系我們修改或刪除:zhangkai@cgbtek.com

COPYRIGHT北京華林嘉業科技有限公司 版權所有 京ICP備09080401號